| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | Quiz | Index |

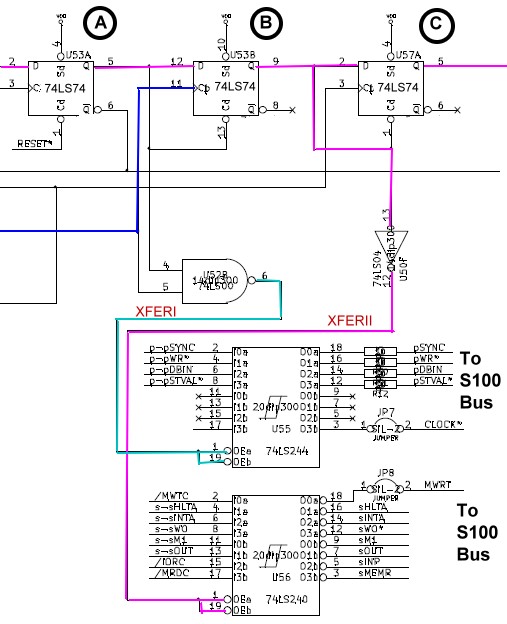

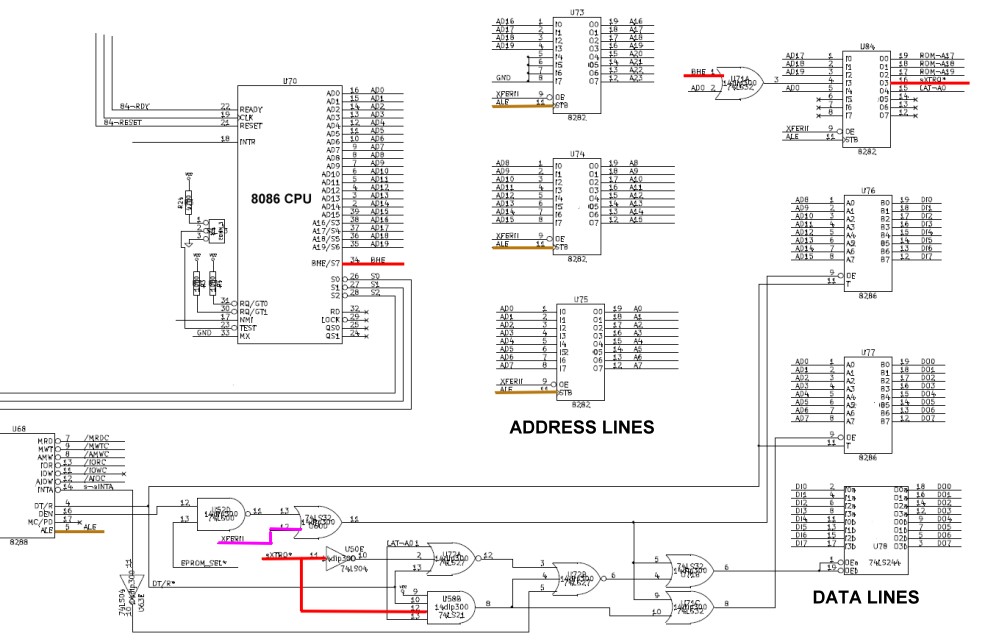

| Switched bus drivers from Intel 8282's & 8686's to the more common (and far less expensive), 74LS373's and 74LS245's. | |

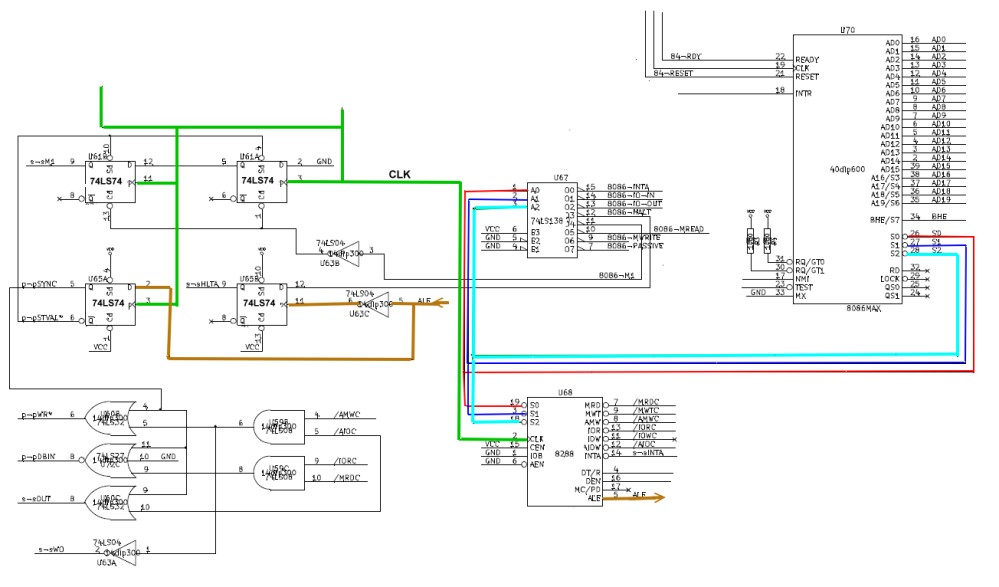

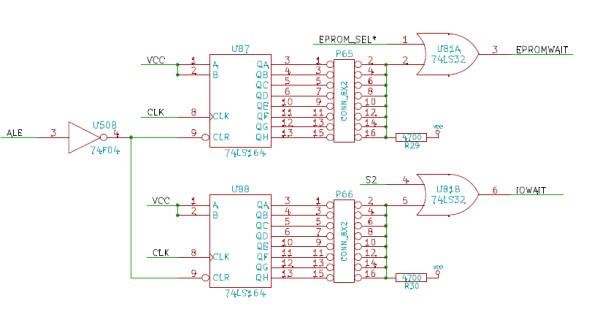

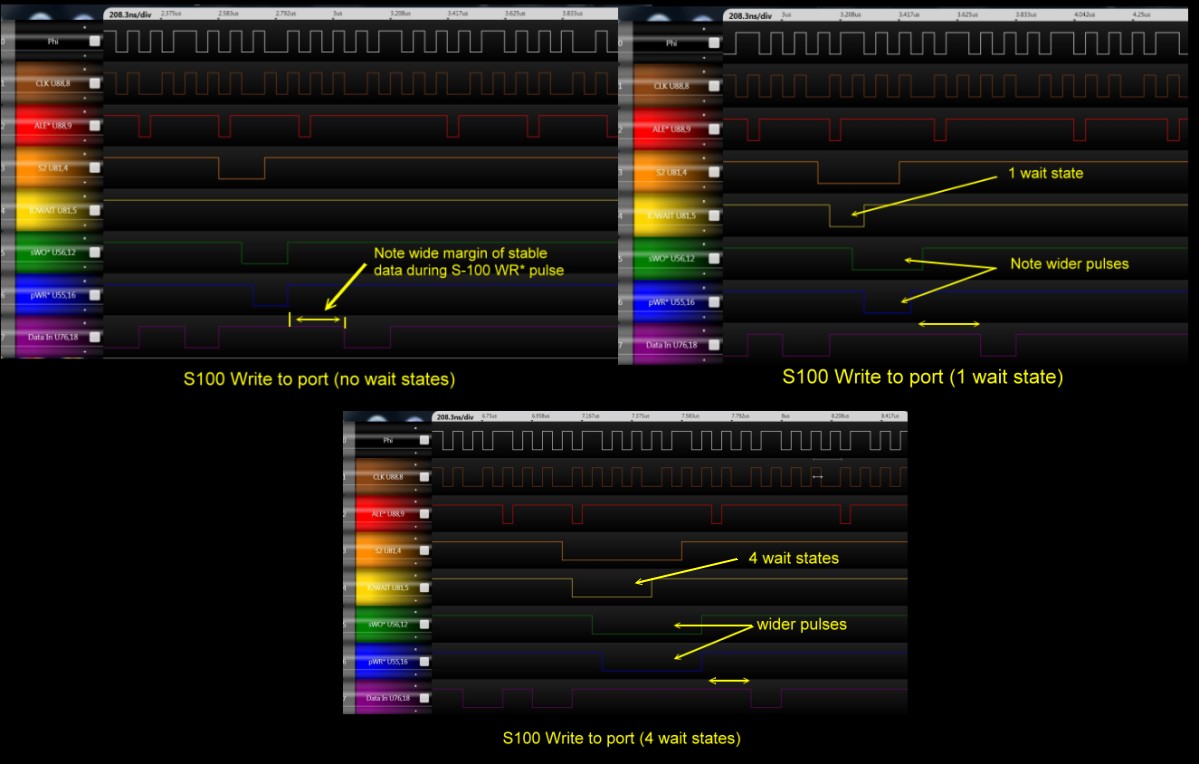

| Completely redid the wait state circuitry (allowing 0 to 8 weight states) for slow old I/O boards and the onboard EEPROM/ROMs | |

| Adding on the board an IO port board circuitry that allows any CPU to switch on the board (no longer need the SMB or an external switch). | |

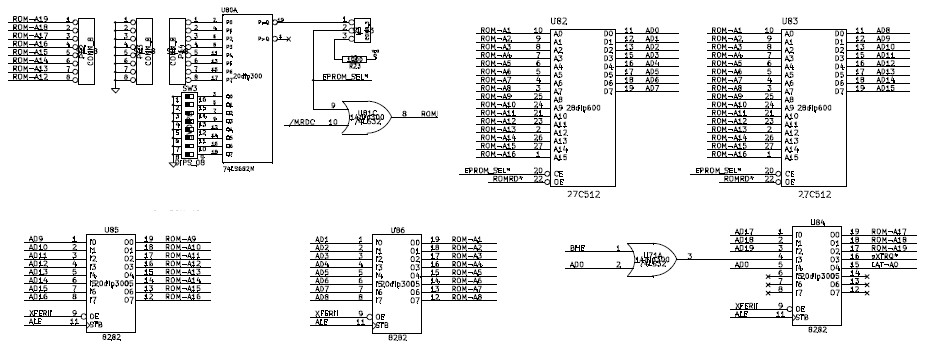

| The board can now utilize either 27C512 (or more practically) 28C64 EEPROMS | |

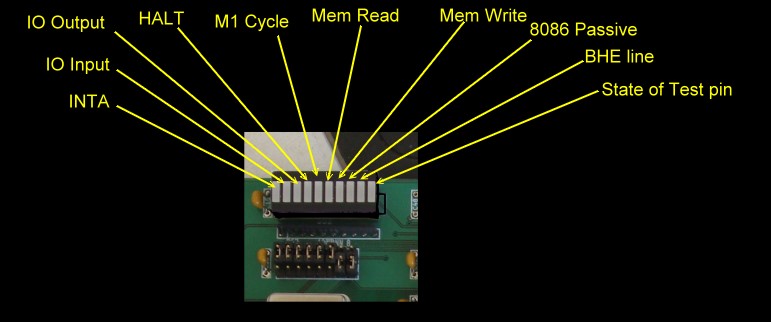

| More LED's to show what is going on. |

This page was last modified on 09/18/2011